台积电董事长刘德音去年9月时所说的一句话,让CoWoS技术再一次成为全球关注焦点:

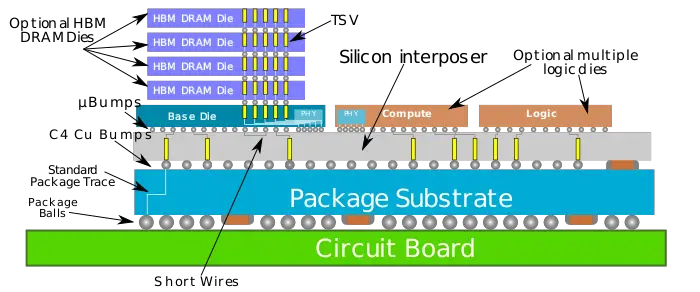

现在AI芯片短缺,缺的不是芯片,而是缺CoWoS封装(如下所示)产能。

时间回到今年3月中旬,日月光高级副总裁Ingu Yin Chang在其分享的《异构集成加速人工智能经济发展》主题演讲中有了更为详细的表述:

世界正在向AI时代迈进,人工智能和数据将继续推动半导体创新,AI芯片于智能手机、自动驾驶、自动化机器人等应用,带动半导体需求成长,到2030年及以后,其指数级增长将塑造全新的生活方式。

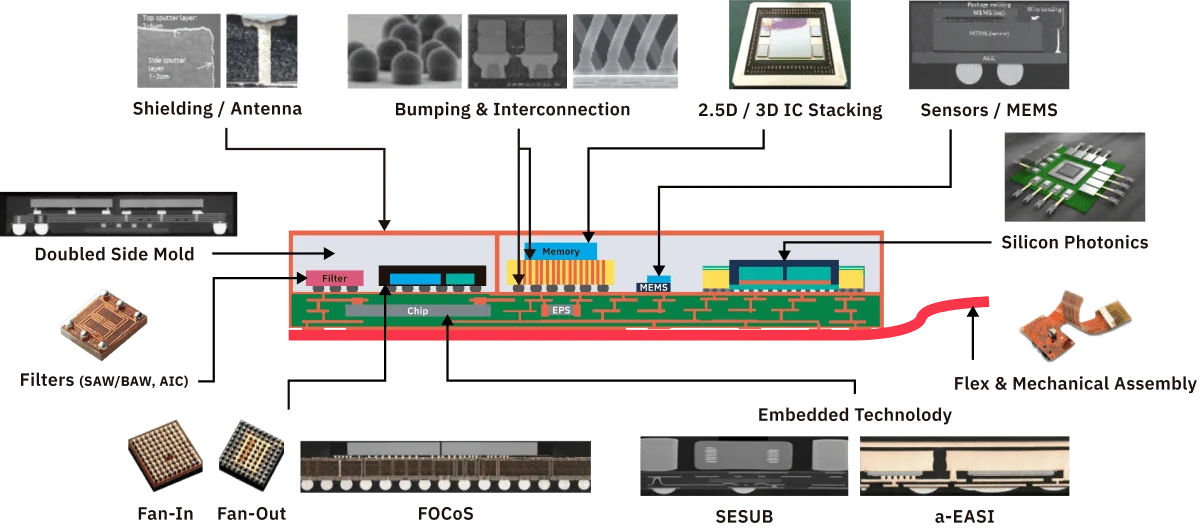

半导体行业正在通过异构集成加速人工智能经济一体化发展;创新的封装方式能够使多个Chiplet、SiP和模块无缝集成到一个封装中,以增强功能性能和操作特性。

针对二位的发言,我们不难看出:一场由CoWoS技术为代表的异质集成技术,或将成为本次AI芯片算力革命的关键节点。

异质集成技术成为AI芯片算力革命关键节点的主要原因在于:它能够解决传统单一芯片设计在性能提升、能效比优化和空间利用率上遇到的物理和技术瓶颈。

或许正是由于以下几个因素共同作用,使得异质集成技术成为了本次AI芯片算力革命的关键节点:

提高计算效率:

异质集成允许将专门的加速器直接集成到处理器旁边,如AI加速器、图形处理单元(GPU)、数字信号处理器(DSP)等,这些加速器可以针对AI算法进行特殊优化,从而显著提高特定任务的计算效率。

例如:TPU(Tensor Processing Unit)就是专为加速机器学习算法而设计的,可以提供比传统CPU更高的性能。

符合低功耗和小型化的需求:

在AI应用中,尤其是在边缘设备上,功耗是一个非常重要的考虑因素。异质集成技术通过优化芯片内部的数据流,减少了数据在不同处理单元间的传输距离,从而降低了功耗。

此外,能够将特定任务交给最适合处理该任务的单元,避免了在不需要时运行高功耗的处理单元,进一步降低了整体功耗。

将不同的处理单元集成到一个芯片上,可以显著减少芯片所需的总面积,这对于需要将大量功能集成在有限空间内的移动设备和穿戴设备尤为重要;这种集成还减少了需要额外封装的独立芯片数量,进一步节省了空间。

提高带宽和减少延迟:

异质集成技术通过在芯片内部创建更短的连接路径,提高了处理单元之间的通信带宽,减少了数据传输延迟。

例如,通过使用硅通孔(Through-Silicon Vias, TSVs)技术,可以在堆叠的芯片层之间直接建立连接,这对于需要高速数据交换的AI应用至关重要。

除上述工技类提升所带来的直观突破外,在AI芯片的发展中,异质集成技术也因以下三点为AI芯片的高度定制化铺平了道路:

针对特定算法和应用的优化:

AI领域涵盖了广泛的应用和算法,每种应用对芯片的要求各不相同。异质集成技术允许在同一芯片或封装内集成专为特定任务优化的加速器(如神经网络处理器NPUs、图形处理器GPUs等),以及针对特定算法优化的逻辑电路。

这意味着可以为深度学习、图像识别、自然语言处理等不同的AI任务定制硬件,从而在算法层面上实现最佳的性能和能效比。

模块化设计:

异质集成技术支持模块化的设计理念,使得芯片设计更加灵活。设计师可以根据最新的技术进展或市场需求,选择最适合的处理单元和存储模块进行集成。

这种模块化设计不仅加快了产品的开发周期,还能在产品发布后快速响应市场变化,通过替换或升级特定模块来提升产品性能或降低成本。

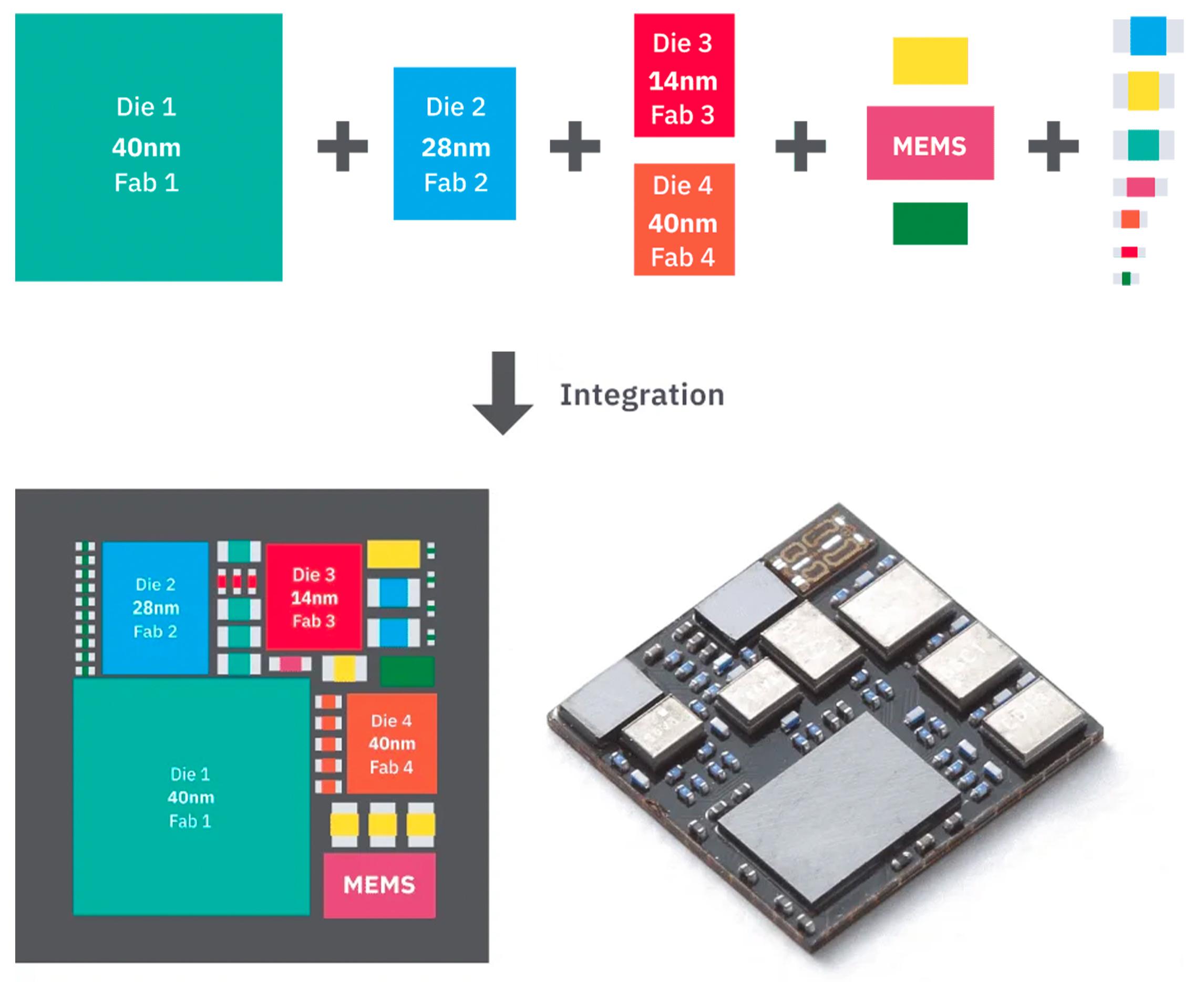

支持多技术节点集成:

异质集成技术使得可以在同一封装中集成不同技术节点的芯片。这意味着即使是使用较老工艺制造的组件(如I/O或模拟信号处理器),也可以与使用先进制程技术制造的高性能计算核心(如CPU、GPU)集成在一起。

这种跨技术节点的集成为产品设计提供了更大的灵活性,使得开发者能够根据性能需求和成本考虑,选择最适合的技术组合。

最近几年,随着异质集成技术的不断发展,异质集成技术或早已落地生花。

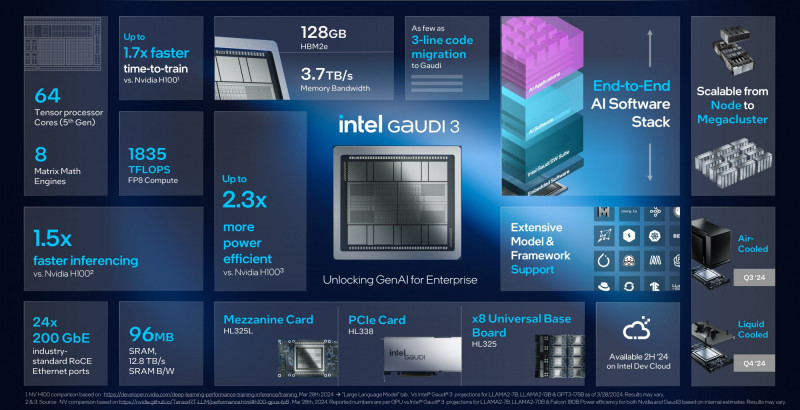

美东时间4月9日周二,在今年举办的客户与合作伙伴大会Intel Vision 2024期间,Intel正式发布第三代Intel AI加速器Gaudi 3也被大众视为异质集成技术的再一次应用落地。

Gaudi 3采用5纳米工艺制造,专为高效的大规模 AI 计算而设计,其具有64个第五代张量处理核心和8个矩阵计算引擎,采用128GB 速率达 3.7TB / s 的 HBM2e 内存和 96MB 速率达 12.8TB / s的SRAM,还具有24个200 Gbps以太网RDMA NIC以及最高 16 条 PCIe 5.0 总线。

对比英伟达的芯片H100,如果应用于7B和13B参数的Meta Llama2 模型以及175B参数的OpenAI GPT-3模型中,Gaudi 3预计可以让这些模型的训练时间平均缩短50%。

应用于7B和70B参数的Llama以及180B参数的Falcon模型时,Gaudi 3的推理速度相比英伟达H200提高30%。

不光Intel,异质集成技术或早已成为多个大厂看门绝技,尤其在多个芯片高速互连集成中表现突出:

NVIDIA:NVIDIA使用异质集成技术开发了一系列高性能的GPU和AI加速器,如NVIDIA Tesla V100和A100。这些产品采用NVIDIA的NVLink技术,可以将多个GPU通过高速互连集成在一起,提供前所未有的并行计算能力。

Google :Google的Tensor Processing Unit(TPU)是专为加速机器学习应用而设计的AI处理器。TPU采用异质集成技术将高性能的计算核心与大量的内存集成在一起,以优化机器学习任务的处理速度和能效。

AMD的芯片封装技术:AMD采用了类似的异质集成技术,在其Ryzen和EPYC处理器中集成了多个计算核心芯片,以及用于高速缓存和I/O的单独芯片,通过Infinity Fabric互连技术实现高效通信。

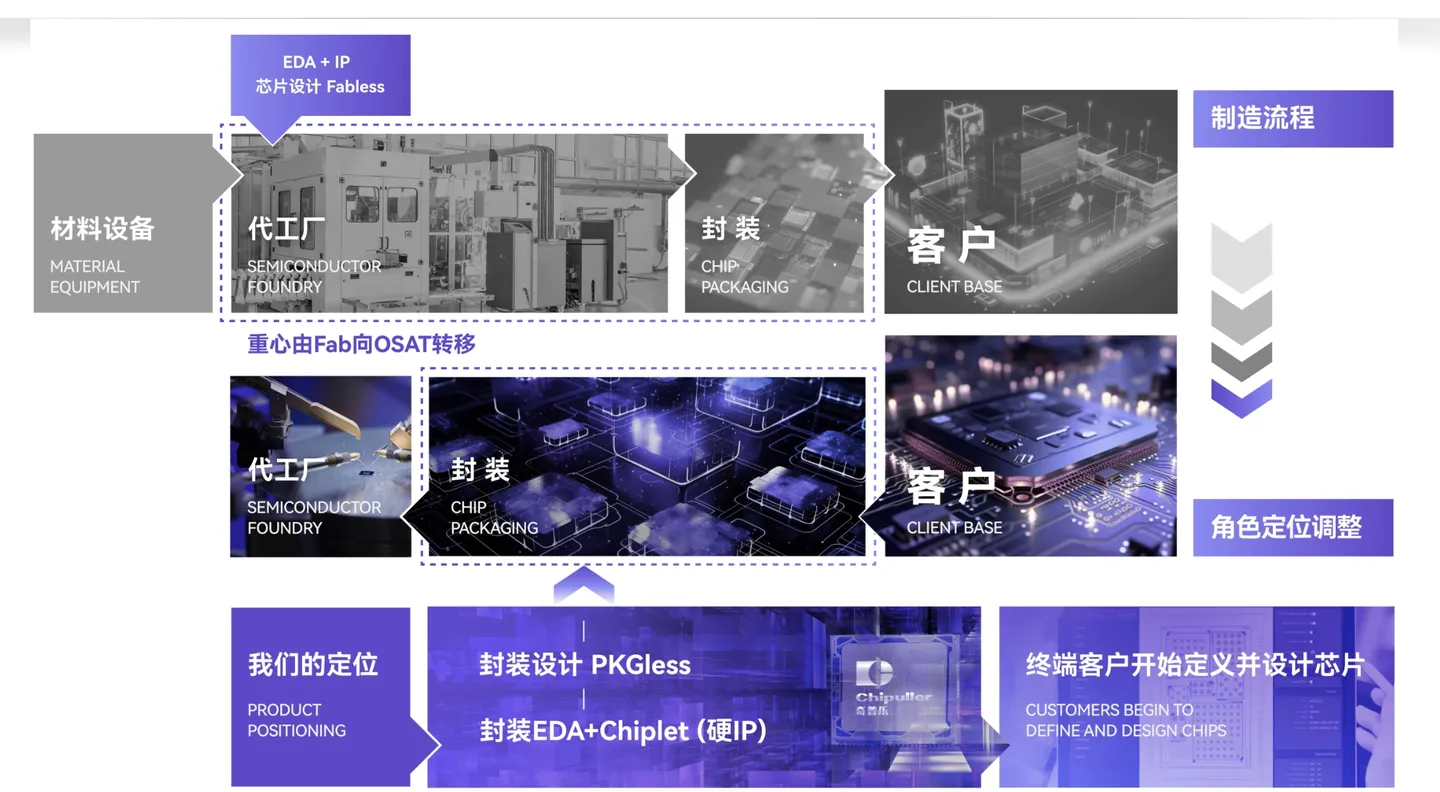

与此同时,或许就在今天,异质集成技术的发展也促进了芯片设计领域一个重要转变:即从传统的通用处理器设计向客户和终端应用定制化设计的转移。

这种转变体现在芯片设计不再仅仅追求通用性和广泛适用性,而是越来越多地考虑到特定应用需求、性能优化、能效比提升和成本效益。

众所周知,Chiplet技术作为异质集成技术的集大成者,它的应用使得芯片的开发周期大大缩短,进一步加速了产品的生产时间;在此之上,例如Chipuller(奇普乐)自研的Chipuller 1.0等芯片设计平台,已经可以支持终端用户在Web端体验一个简单而高效的定制流程。

在面向多元化的应用设计方面:

异质集成技术通过将具有不同功能的组件(如CPU、GPU、DSP、AI加速器等)集成到同一芯片或封装中,使得设计师可以针对特定应用或任务优化芯片。

这种优化不仅涉及提高计算效率和处理速度,也包括能耗、热管理和成本。因此,芯片设计开始更多地从终端应用和客户需求出发,而非仅仅基于技术可行性。

当然这种由异质集成技术所带来的新理念,或许也有着降本增效的作用:

在传统芯片设计中,技术迭代和升级往往需要重大的时间和成本投入;而异质集成技术使得在现有设计框架内部署新技术或更新组件变得更加容易和经济。

这种快速迭代能力不仅加速了技术发展,也使得终端产品能够更快地适应市场变化和技术进步,提供给客户更多的选择和更好的性能。

综上所述,我们不难看出:异质集成技术不仅是一种技术进步,也代表了芯片设计哲学的转变。

它将客户和终端应用的需求置于设计的核心,通过提供高度定制化和灵活的解决方案,推动了个性化和功能特定化的产品开发。这种设计思想的转变有望进一步推动技术创新,为用户带来更多高效能、低功耗且功能强大的电子产品。

由于篇幅受限,本次异质集成技术就先介绍这么多......

想了解更多半导体行业动态,请您持续关注我们。

奇普乐将在每周,不定时更新~

最后的最后,借由歌德的一句名言:

大胆的见解就好比下棋时移动的一颗棋子,它可能被吃掉,但它却是胜局的起点。

愿每一位半导体从业者可以——

铎己以新,不以足己!